# 薄型 WLP-IC 内蔵ポリイミド多層配線板

電子デバイス研究所 佐野 宜紀1・岡本誠裕1・奥出 聡2

# Thin WLP-IC-Embedded Polyimide Multilayer Printed Wiring Board

Y. Sano, M. Okamoto, and S. Okude

電子機器の小型化を実現するための高密度実装方式として,ICをポリイミド多層基板内部に埋設するIC内蔵ポリイミド多層基板を開発した.ポリイミドフィルムを用いた多層配線板の技術とICへの 薄型ウエハレベルパッケージ(WLP)技術を融合させることで,総厚220 μmの薄型基板を実現している.本稿では,薄型でフレキシブルであるという特長が基板特性に与える影響について報告する.

We have developed an IC-embedded polyimide multilayer wiring board for downsizing electronic equipments. Combining an ultrathin wafer-level package (WLP) technology and a multilayer wiring board technology utilizing polyimide film, a low-profile embedded board with a thickness of 220  $\mu m$  is realized. In this paper, we report the effect of ultrathin and flexible features of the board on its performance.

## 1.ま え が き

近年,電子機器の小型化にともなって,電子部品の高密度実装に対する要求が高まっており,これにこたえる方法の一つとして,電子部品を平面的な配置から3次元的に実装する技術開発が進展している.このような3次元実装を実現する方式として,電子部品をプリント配線板内部に埋設する部品内蔵基板技術が注目を集めている.この技術を用いると,従来のプリント配線板の表層に実装されていた部品の一部を配線板の内部に実装基板の面積を大幅に縮小することによって,実装基板の面積を大幅に縮小することが可能となる.内蔵する電子部品としては,抵抗器やコンデンサなどの受動素子,能動部品であるIC等が検討されており,様々な種類の部品形態とその内蔵方式が提案されている.

そのような中で,われわれは層間の接続に導電性ペーストを用いたポリイミド多層配線板の技術を用いた IC 内蔵基板を開発した <sup>1)</sup>. この IC 内蔵基板は,ウエハレベルでの加工によって再配線が形成された IC (Wafer Level Packaged IC, 以下 WLP-IC)を 100 μm 以下の薄型に加工 <sup>2)</sup>してポリイミド多層配線板に内蔵する技術である.従来の部品内蔵技術では,部品の埋め込みによる基板総厚の増大が不可避であったが,薄型フィルムであるポリイミドに薄型加工した IC を内蔵することで,

## 2.薄型 WLP-IC 内蔵ポリイミド多層配線板

## 2.1 構造とプロセス

われわれが開発した IC 内蔵基板の断面模式図を図1に示す.WLP 技術によって銅再配線の形成された IC が,ポリイミドを絶縁層とした多層配線板の内部に内蔵されている.多層配線板の層間および内蔵 WLP-IC の周囲は接着材で隙間なく充填されており,配線層間の電気的な導通および内蔵 WLP-IC と配線層との電気的な導通は,導電性ペーストによってなされている.この IC 内蔵基板は,以下のプロセスによって作製される.

図 1 WLP-IC 内蔵基板の断面構造模式図 Fig. 1. Cross sectional schematic of a WLP-IC embedded wiring board.

基板総厚の増大を最小限に抑え,最小で220 μm厚のIC 内蔵基板を実現した.ベースとなるポリイミドフィルムは,フレキシブル配線板などに使用される材料であるため,IC 内蔵基板は可撓性を有しているが,これは外部からの曲げにより内蔵 WLP-IC も曲がることを意味しており,その特性への影響が懸念される.今回,IC 内蔵基板の耐曲げ性を限界曲げ試験によって検証したので,その結果について報告する.

<sup>1</sup> マイクロデバイス開発部

<sup>2</sup> マイクロデバイス開発部 グループ長

略語・専門用語リスト 略語・専門用語 正式表記 説 明 WLP 半導体のウエハ状態で樹脂封止と端子形成を行う Wafer Level Package 半導体のパッケージング方法 . IC 製品を半導体チ ップ程度に小型化できる. CCL 銅張積層板 Copper Clad Laminate デイジーチェーン Daisy Chain ビアを介して数珠繋ぎに接続された一続きの回路 設計上・製造上の問題を見つけ出すための専用回 TEG Test Element Group 路を設けた評価用素子

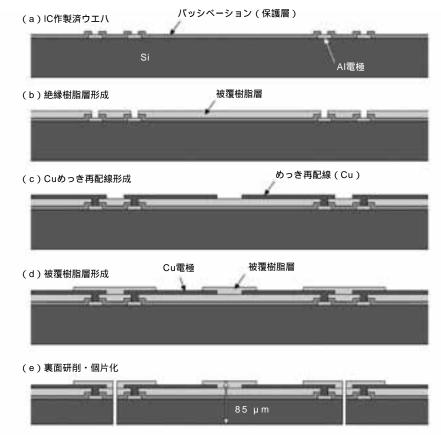

図2 内蔵用 WLP-IC の作製工程 (IC ウエハ断面模式図)

Fig. 2. Fabrication process of WLP-IC for embedded boards. (Cross sectional schematic of an IC wafer).

### (1) 内蔵用 WLP-IC 作製のプロセス

多層配線板に埋め込む IC のウエハレベルにおけるプロセスを図 2 に示す・同図 (a) に示すような IC 作製済みのウエハ上に , (b) 感光性樹脂を用いてフォトリソグラフィーにより IC 電極部を開口して絶縁樹脂層を形成する・次に , (c) セミアディティブ法によって銅再配線を形成して , (d) 樹脂封止をすることで銅電極が形成される・最後に , (e) IC 裏面を研削することで 85 μm に薄型化して , 個片化を行うことで内蔵用 WLP-IC が完成する・

#### (2) WLP-IC 内蔵のプロセス

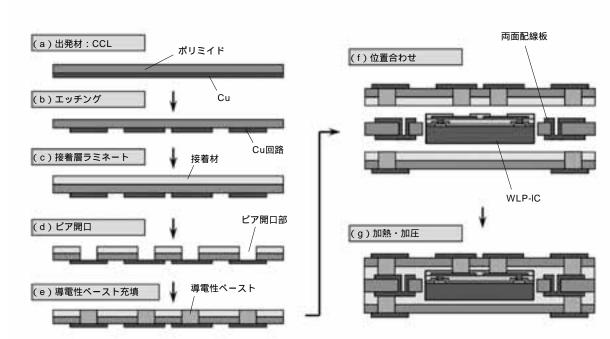

次に、プリント配線板にWLP-ICを内蔵するプロセスを図3に沿って説明する.同図(a)に示すような銅箔が貼り合わされたポリイミド絶縁基材(CCL)を出発材として、(b)銅をエッチングすることで回路を形成する.続いて、(c)層間を接合するための熱硬化性接着材を貼り合わせ、(d)レーザによるビア開口をして、(e)スクリーン印刷による導電性ペーストの充填を経てビアを形成する.

以上のプロセスによって作製された WLP-IC,ペース

図3 基板の多層化と WLP 埋め込みプロセス(基板断面模式図)

Fig. 3. Fabrication process of WLP-IC-embedded multilayer boards. (Cross sectional schematic of a wiring board.)

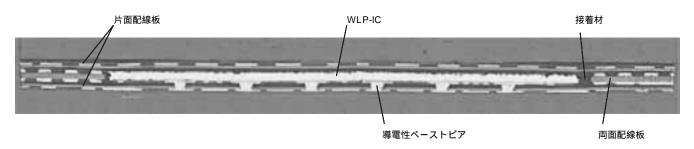

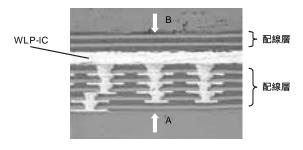

図4 WLP-IC 内蔵基板の断面写真 Fig. 4. Cross sectional photograph of a WLP-IC-embedded wiring board.

トビアの形成されたプリント配線板,および内蔵するWLP-ICを配置するスペースが設けられた両面プリント配線板を(f)位置合わせし,(g)全体を一括で加熱・加圧する.このプロセスにより,以下が同時に達成される.

- (i) WLP-IC の周囲が接着材の流動で隙間なく充填された後に、その硬化によりプリント配線板および内蔵WLP-IC が一体化する.

- (ii) 導電性ペーストの焼結合金化によって,プリント配線板の配線層間が電気的に接続される.

- (iii) 同様に, WLP-IC の銅電極と配線板の配線層が電気的に接続される.

以上によって,薄型 WLP-IC 内蔵基板が完成する.このプロセスは,層間の電気的な接続に導電性ペーストを用いたポリイミド多層配線板のプロセスをそのまま適用することが可能であり,基板内蔵のための特殊なプロセスなしに WLP-IC の基板埋め込みを実現している.

#### 2.2 特 徵

以上のプロセスによって作製された IC 内蔵基板の断

面写真を図4に示す.内蔵WLPの周囲が接着材で隙間なく充填され,表層の平坦性も良好であることがわかる. 本開発品の特徴は以下のとおりである.

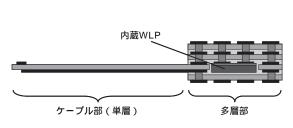

## (1)フレキシブル材の使用および配線板の薄型化

裏面を研削した WLP-IC を薄型のポリイミドを基材とした多層配線板に内蔵することで,図 1 に示す 4 層構造の配線板で基板厚さ 220  $\mu$ m を達成している.これは報告されている他の IC 内蔵基板  $^{3)}$  と比べても半分以下の薄さである.さらに,基材のポリイミドは可撓性を有するので,図 5 に示すような柔軟性を有するフレキシブル配線板(ケーブル部)との一体構造とすることが可能である.これは,部分的に多層化して WLP-IC を埋め込むことにより比較的容易に実現できる.

# (2) WLP **加工した** IC **の内蔵**

銅再配線を形成することで、比較的狭ピッチなICの電極間隔がプリント配線板プロセスに適用可能なレベルに拡大される.さらにIC端子は銅電極になる.従来開発されてきたポリイミド多層配線板では、銅と金属粒子が加熱によって合金化する導電性ペーストを使用して

図 5 ケーブル一体化構造 Fig. 5. Cable unified structure.

図 6 8 mm 角 WLP 内蔵基板の断面写真と曲げ方向 Fig. 6. Cross sectional photograph of an 8 mm WLP-IC embedded board.

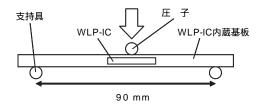

図7 限界曲げ試験条件 Fig. 7. Limit bending test of WLP-IC.

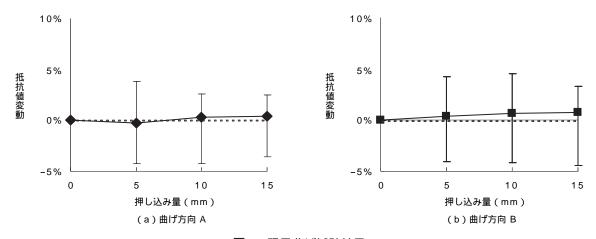

図8 限界曲げ試験結果 Fig. 8. Result of limit bending test of WLP-IC.

おり<sup>4)</sup>, したがって, 内蔵 IC と配線層が導電性ペーストにより接続可能になる.また,被覆樹脂層によって保護されることで, IC 埋め込みプロセスでの取り扱いが容易になるとともに, IC の動作を事前に確認して良品のみを内蔵することが可能である.

# 3. 限界曲げ試験

われわれが開発した IC 内蔵基板は,可撓性を有するポリイミドを基材としているので,曲がりやすいという特徴をもっている.しかし,これは基板のハンドリングや機器内への実装時に基板が曲がりやすいということを意味しており,曲げによるストレスで WLP-IC や導電性ペーストビアが破壊されてしまうことが懸念される.

そこで,機械的な信頼性を確認するために IC 内蔵基板を用いて曲げ試験を実施し,曲げによるストレスが基板性能に与える影響を調査した 5),6).

評価に使用した WLP-IC 内蔵基板の断面写真を図 6 に示す. 内蔵した WLP-IC の大きさは 8 mm 角で 85  $\mu$ m 厚に薄型加工されており, IC 電極側 (IC 下側) に 5 層, 裏面側 IC 上側)に 2 層の配線層が積層されている. また, 内蔵 WLP-IC は TEG であり, WLP-IC の銅再配線と配線板銅回路からなるデイジーチェーン回路が導電性ペーストビアを介して組み込まれており,抵抗値による特性評価が可能である.

試験は3点曲げ法で図7に示す条件で行い,押し込み量5 mm,10 mm,15 mmの3段階で曲げ試験を実施し,外観および試験前後の抵抗値変化で評価した.試

験前後の抵抗値変動を図8(a),(b)に示す.図6中Aの方向から圧子により15 mmの押し込みを行っても,デイジーチェーン回路抵抗値の変化は最大で5%以内であった.この変化は測定誤差の範囲であり,曲げによって導電性ペーストビアによる接続は影響を受けないことを確認した.また,埋め込みICチップに割れは発生しなかった.

さらに,逆方向(図 6 中 B)からの押し込みも同様の条件にて実施した結果(図 8 (b)),15 mm までの押し込みに対してもデイジーチェーン回路抵抗値の変化は最大 5 % であった.また,埋め込み IC チップに割れは発生しなかった.

今回の限界曲げ試験においては、15 mm以上の押し込み量に対しては試験装置と基板の制約により有効な結果を得る試験ができなかったため、基板が破壊される限界値はわからなかったが、実環境において生じる曲がりはこれらの試験レベルより充分小さいので、実際の使用環境においての曲げによる特性変動は殆どなく、問題は無いと考えられる。

このように開発した IC 内蔵基板が高い曲げ耐性を有するのは,(1) IC を薄くすることで IC チップにかかる応力が破壊するレベルよりも十分小さくなっていること(2) 導電性ペーストについては,弾性率の低い樹脂成分も含まれているので,曲げによりかかる応力を緩和していること<sup>7)</sup>などの理由によると考えている.

### 4.む す び

ポリイミド多層配線板へ WLP-IC を内蔵した薄型 IC 内蔵基板を開発した.ポリイミドフィルムを基材とし, 内蔵 IC を薄型加工することで,4 層構造の部品内蔵基板で厚さ220 μm を達成した.薄型化により曲がりやすくなることで,基板の曲げが性能に影響を与えることが懸念されたが,限界曲げ試験により実用上問題がないことを確認した.われわれの開発したIC 内蔵基板は単に部品内蔵により実装密度を上げるだけでなく,FPCの持つフレキシビリティを併せ持つことができるため,従来にない電子部品の実装形態を提供可能な高密度実装技術であり,電子機器の更なる小型化に貢献できると考えている.

## 参 考 文 献

- 1) 岡本ほか:「IC 内蔵基板」, フジクラ技報,第111号, pp.54-58,2006

- 2) 石塚ほか:「表面実装用極薄型 WLP」, フジクラ技報, 第117号, pp.48-53, 2009

- 3) 福岡ほか:「受動チップ部品/能動デバイス混載内蔵配線板の開発と実用化」,エレクトロニクス実装学会誌, 第11号,No.4,pp.260-270,2008

- 4) 本戸ほか:「全層ポリイミド多層配線板の信頼性」, フジクラ技報,第116号, pp.43-47, 2009

- 5) 佐野ほか:「薄型 WLP-IC 内蔵ポリイミド多層配線板」, 第 23 回エレクトロニクス実装学会講演大会論文集, 13C-03, 2009

- 6) 佐野ほか:「導電性ペーストビアを用いた IC 埋め込み 基板」,第16回エレクトロニクスにおけるマイクロ接 合・実装技術シンポジウム論文集,Vol.16,pp.375-378, 2010

- 7) 奥出ほか:「ウェハレベルパッケージ技術を用いた IC 内蔵ポリイミド多層配線板」,電子情報通信学会論文誌,Vol. J92-C No.11, pp.664-670, 2009